現代科技不斷革新,網路平台與雲端運算背後,仰賴著上千台電腦伺服器相互連結;智慧型手機除了能登錄網頁與多樣化的應用程式,未來更能支援擴增實境 (AR)、3D影像、支付等功能;除此之外還有感測元件、智慧家庭、穿戴式裝置、自動車…。

從電子商務、金融到醫療、法務,所有產業正面臨著大規模的劇變。科技的浪潮提供更便利的社會,為人類生活帶來了無限的可能;支撐這一切發展的基石,就是「半導體」。

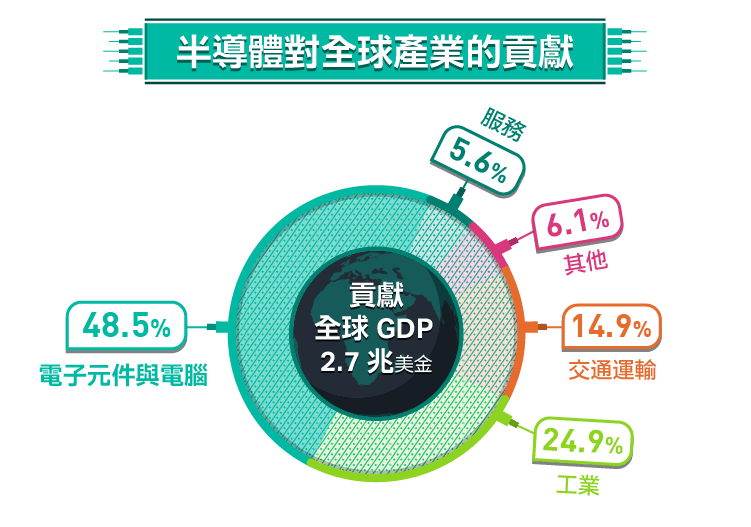

在全球經濟體中,半導體相關產業每年帶來的經濟效益約是 7 兆美元;而在2012年,台灣半導體總產值突破 2 兆台幣,躍居世界第 2 位、成為最大的產業群,就業人次高達18萬。電子類股也在台灣股市中佔了高達 66% 的最大產業類股權重。

在全球經濟體中,半導體相關產業每年帶來的經濟效益約是 7 兆美元;而在2012年,台灣半導體總產值突破 2 兆台幣,躍居世界第 2 位、成為最大的產業群,就業人次高達18萬。電子類股也在台灣股市中佔了高達 66% 的最大產業類股權重。

作為台灣人,不可不知半導體。(按曰:十萬青年十萬肝,GG輪班救台灣)

時常在報章雜誌上聽到半導體、晶圓、IC、奈米製程等名詞,卻又不甚了解意思?

本系列的 IC 產業地圖,將以半導體相關知識作為系列首篇,介紹「晶圓代工」相關名詞與各國間產業現況。並討論各大廠間的競合關係。

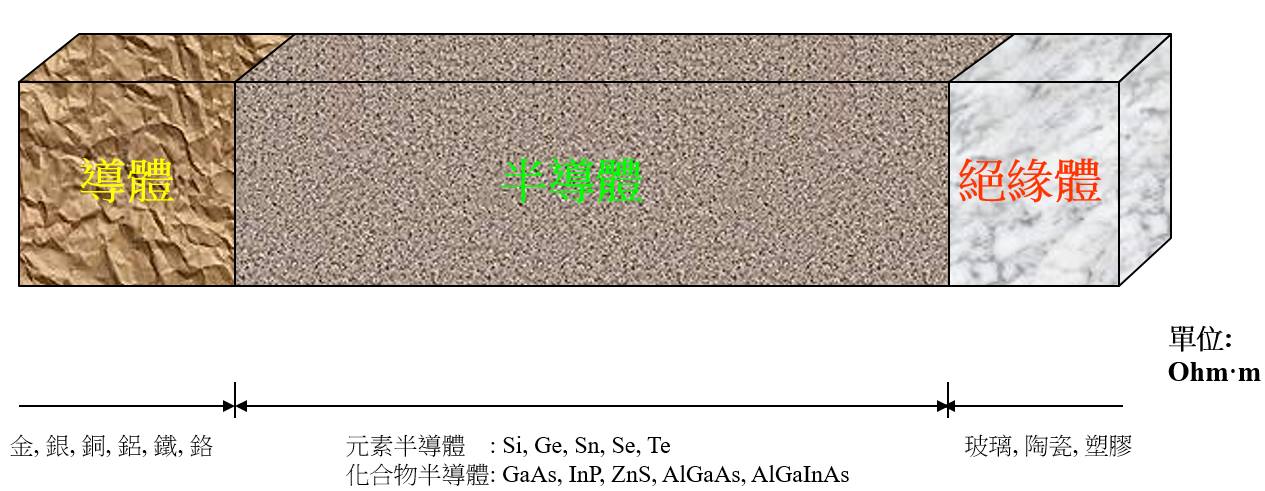

什麼是半導體?

半導體是導電性介於導體(金屬)與絕緣體(陶瓷、石頭)之間的物質,包括矽、鍺。

利用半導體製作電子元件的目的在於:不像導體絕對導電、絕緣體完全不導電;藉由注入雜質,可以精準地調整半導體的導電性。由於矽擁有較大的能隙、可以有較大雜質摻雜範圍,所以可以被利用來製作重要的半導體電子元件電晶體 (Transistor)。

由於發明了電晶體,這個年代成為人類科技文明進步最快的年代,電子技術與電腦工業才開始了長足的發展,堪稱二十世紀最偉大的發明之一。

發明電晶體的蕭克利 (Shockley)、巴丁 (Bardeen) 與布拉頓 (Brattain) 三位物理學家在1956年共同榮獲諾貝爾獎。

1956年,蕭克利在舊金山南方成立蕭克利半導體實驗室 (Shockley Semiconductor Lab),帶動美國矽谷 (Silicon Valley) 的蓬勃發展,矽谷一名稱係由半導體原料矽而來。

講到矽谷的發展成因與歷史,絕對不能不提蕭克利半導體實驗室的影響。一個天才的創業會引來眾多天才的投奔,因此當時一堆優秀人才趨之若鶩地跑到蕭克利的實驗室來;但後來因蕭克利暴躁又疑神疑鬼的性格,又紛紛辭職離去,被蕭克利怒稱為「八叛徒」(The Traitorous Eight)。

八位叛徒中,包括了諾伊斯 (Noyce)、摩爾 (Moore,就是摩爾定律的那個摩爾!) 等人,他們隨後成立了快捷半導體 (Fairchild Semiconductor),成為了第一家將矽電晶體商業化的公司。

這家公司最重要不是它的產品、而是影響力——快捷可說是矽谷人才的搖籃,創始人和員工出來開的公司和投資的公司在灣區超過 130家上市企業,裡面包括了 Intel、AMD 等公司,市值達 21 萬億美元。對矽谷乃至當今時代的科技發展都有著不可或缺的影響和作用。

此為後話不提,讓我們回來看看矽谷發展一切的源頭——電晶體到底是什麼。

電晶體的主要功能有兩個:「放大信號」與「開關」。

電晶體就像是數位訊號的「收音機」──收音機的原理是將微弱的訊號放大、用喇叭發聲出來,電晶體能將訊號的電流放大;而數位訊號是由0與1組成,1代表著電流「開」、0代表著電流「關」,電晶體以每秒超過 1千億次的開關來運作,讓電流以特定方式通過。

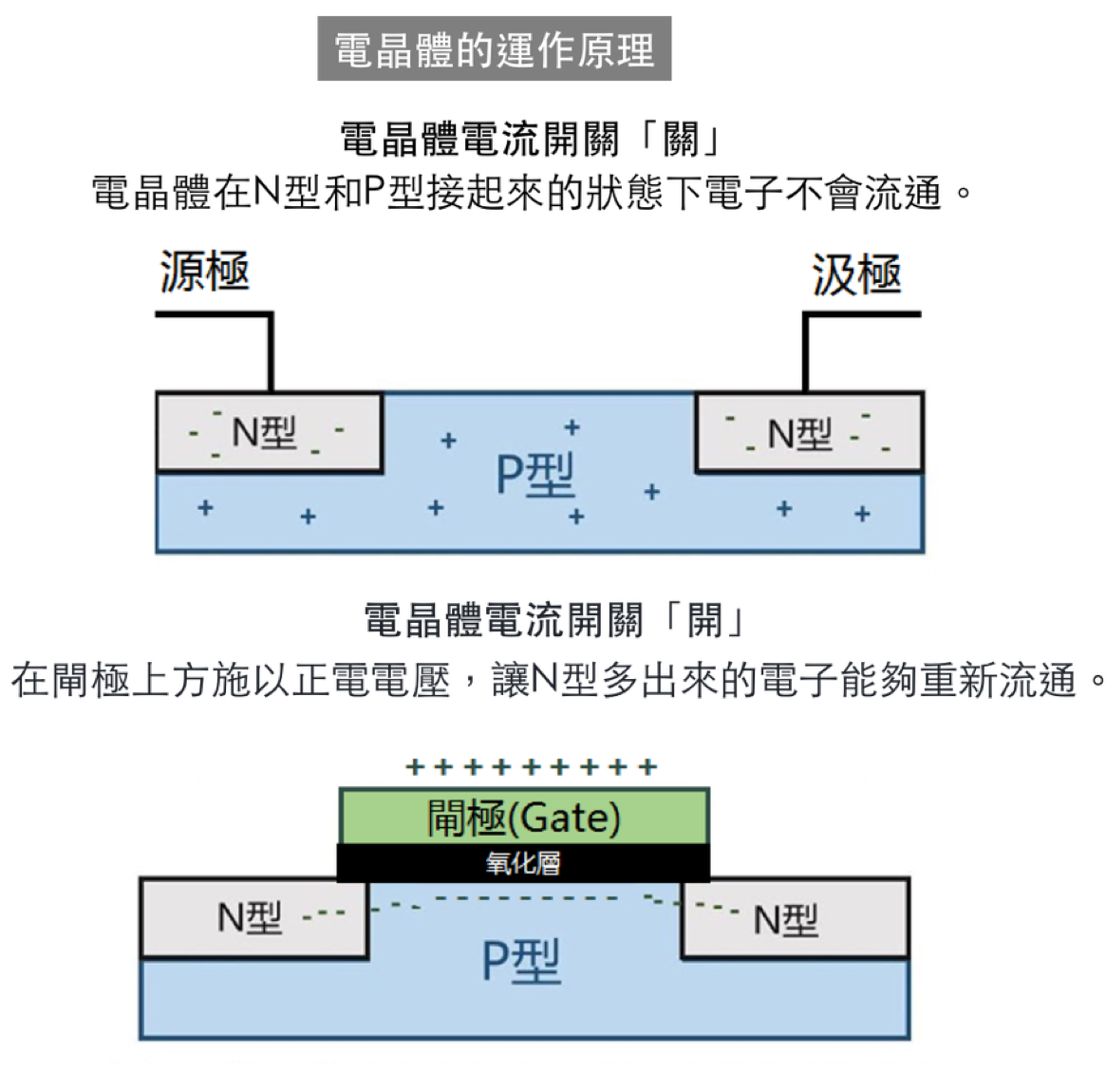

這邊讓我們來簡單談談電晶體的運作原理。

電晶體由矽組成,而矽是 4 顆電子。在矽半導體中加入元素磷,具有 5 顆電子、比矽多一顆電子(-)變成 N 型電晶體 (Negative)。

另外加入元素硼,具有 3 顆電子、 比矽少一顆電子(-)變成 P 型電晶體 (Positive) 。電晶體兩端可以通電,稱為「源極」和「汲極」。

由於P型和N型分別多了電子和少了電子,所以電晶體在 N 型和 P 型接起來的狀態下電子不會流通,此時電流開關為「關」。

為了達到開關的效果,我們使用第三個電極「閘極」(Gate) 取代機械按鈕開關;閘極間以氧化層和半導體隔絕。若我們在閘極上方施以正電電壓,讓 N 型多出來的電子能夠重新流通、並從源極流到汲極,此時電流開關為「開」。

上述即為半導體元件電晶體如何藉由加入雜質(磷、硼)來控制導電性、進而控制電流開關的原理。但是這數億個電晶體在哪裡呢?你可能正在心想:「我手機有大到能放進數億個電晶體?」

答案是:電晶體是奈米等級,比人體細胞還要小。三星以及台積電在先進半導體製程的 14 奈米與 16 奈米之爭,14 奈米指的就是電晶體電流通道的寬度。寬度越窄、耗電量越低;然而原子的大小約為 0.1 奈米,14 奈米的通道僅能供一百多顆原子通過。故製作過程中只要有一顆原子缺陷、或者出現一絲雜質,就會影響產品的良率。

對於半導體大廠而言,製程是技術,但良率才是其中的關鍵 Know-how。一般能將良率維持在八成左右已經是非常困難的事情了,台積電與聯電的製程良率可以達到九成五以上,可見台灣晶圓代工的技術水平。

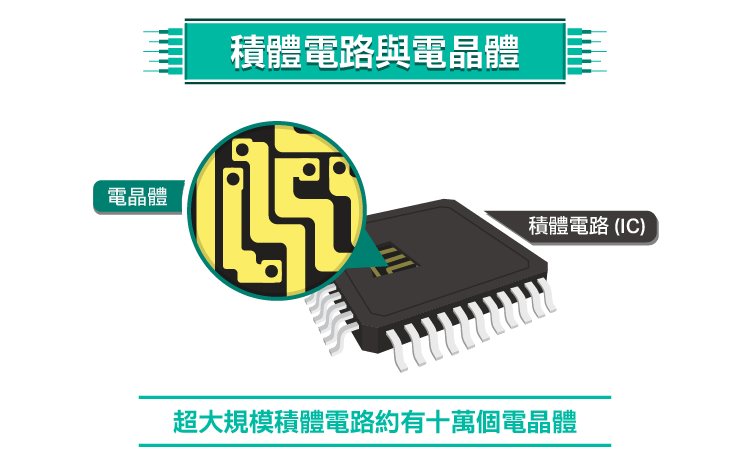

事實上,這數億個電晶體,全部都塞在一個長寬約半公分、指甲大小的晶片上。這片晶片包含電晶體等電子元件,就叫做「積體電路」(Integrated Circuit, IC),俗稱IC。

所謂的大規模積體電路 (LSI, Large Scale Integration) 代表的不是這個電路板很大,而是上面約一萬個電晶體;超大規模積體電路 (VLSI, Very Large Scale Integration) 則約有十萬個電晶體。

積體電路是怎麼製作出來的呢?

在積體電路出現之前,工業界必須各自生產電晶體、二極體、電阻、電容等電子元件,再把所有元件連接起來做成電路,不但複雜又耗時費工。

故若能直接依照設計圖做出一整個電路板,將能更加精確、速度更快且成本更低。

德州儀器公司的基爾比 (Jack St. Clair Kilby) 是第一個想到要把元件放到晶片上集體化的發明人,在 1958 年他試驗成功,開闢了一個嶄新的電腦技術時代。

甚至很多學者認為由積體電路所帶來的數位革命是人類歷史中最重要的事件。基爾比也因此於 2000 年獲得諾貝爾物理獎。

積體電路的製作過程分為以下步驟。

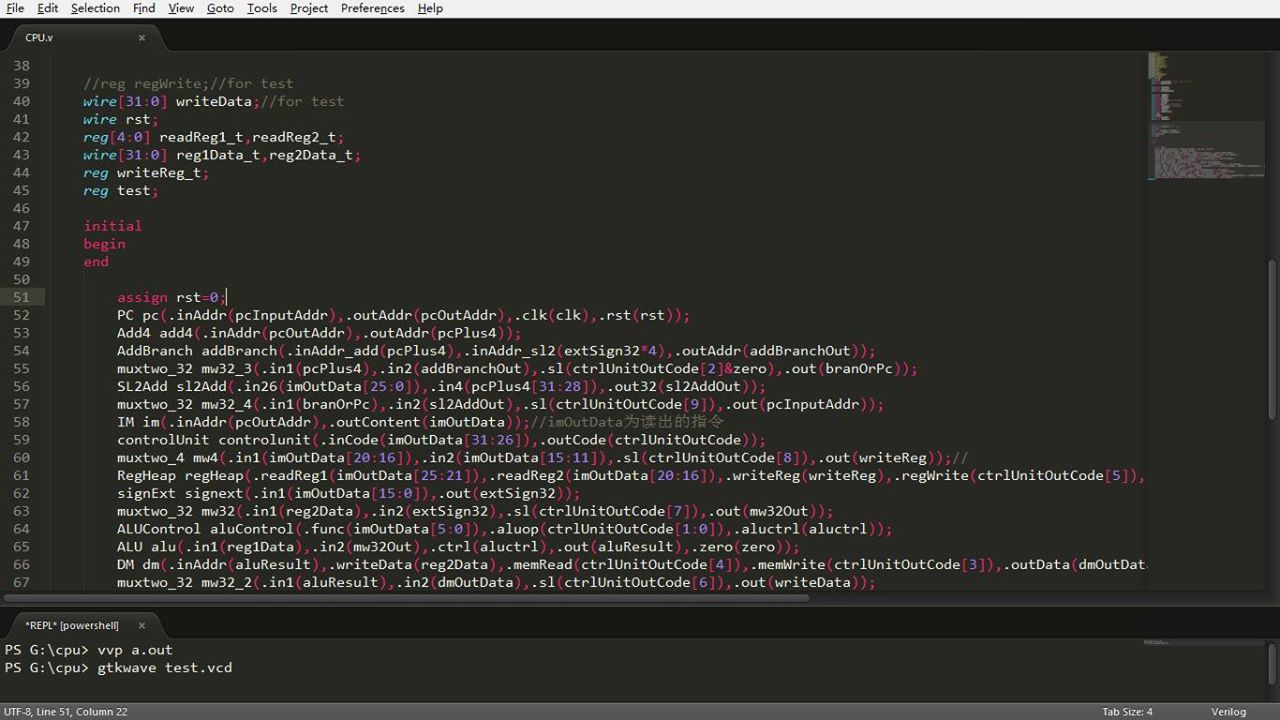

一. 建築設計: IC 設計 (Circuit Design)

如同在蓋房子之前,建築設計師必須畫出設計圖,規劃房間分布、使用材料;在製作半導體晶片時,工程師會畫出電路圖 (Circuit Diagram),規劃一個晶片上應該要具備的功能 (包括算術邏輯、記憶功能、 浮點運算、 數據傳輸)、各個功能分布在晶片上的區域,與製作所需的電子元件。

接下來,工程師會使用硬體描述語言 (HDL) 將電路圖描寫出來。

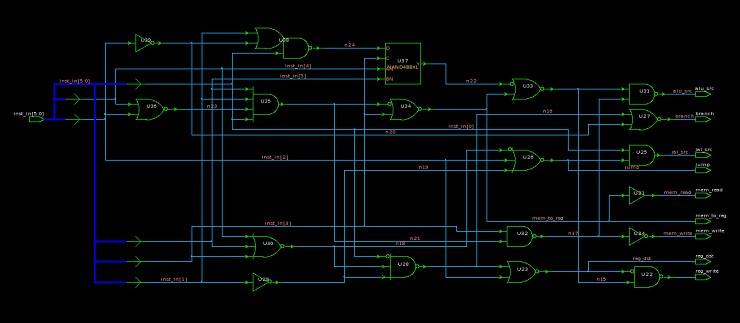

待確認無誤後再將 HDL 程式碼放入電子設計自動化工具 (EDA tool),讓電腦將程式碼轉換成電路圖。

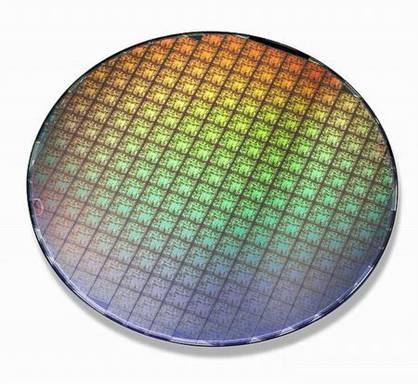

二. 建築地基: 晶圓製造 (Wafer Foundry)

設計師設計完房子後,就需要將電路設計圖交由建築工人將房子蓋出來。蓋房子需要地基,製作晶片也要,安置所有電子元件的基板就是「晶圓」(Wafer)。

首先,晶圓製造廠會將矽純化、溶解成液態,再從中拉出柱狀的矽晶柱,上面有一格一格的矽晶格,後續可供電晶體安置上去。

也由於矽晶格的排列是安裝電子元件的關鍵,「拉晶」的步驟非常重要──晶柱的製作過程就像是在做棉花糖一樣,一邊旋轉一邊成型,旋轉拉起的速度以及溫度的控制都會影響到晶柱的品質。

![]()

接下來,晶圓廠會用鑽石刀像切火腿一般,將一整條的晶柱切成一片片的薄片,再經過拋光後,就變成了「晶圓」(Wafer),也就是晶片的基板;晶圓上面的晶格可供電晶體置入。

晶圓(Wafer)上面的晶格可供電晶體置入。

常聽到的8吋、12吋晶圓廠,代表的就是矽晶柱切成薄片後的晶圓直徑,而整塊晶圓可以再被切成一片片的裸晶 (Die);裸晶經過封裝後,才被稱為晶片 (Chip)、或稱 IC。

晶圓的尺寸,可以決定後續裁切製作出來的晶片有多少數量。

附註: AnySillicon網站上提供的計算機(Die Per Wafer Calculator)可供計算一塊晶圓上能切出多少裸晶。

如直徑8吋的晶圓片使用2.0微米的製程,可以切出588顆64M的DRAM (記憶體);至於12吋的晶圓,可以切出的成品又更多。

然而如先前所述,矽純度、拉晶速度與溫度控制都是晶柱品質的關鍵,越粗的矽晶柱越難拉出好品質,故尺寸越大、技術難度就越高,12吋晶圓廠也就比8吋晶圓廠的製程更先進。

另外,雜質對這些完美無缺的矽晶格構成很大的威脅(想想看:電晶體比人體細胞還小,稍有一絲雜質變足以毀壞整個矽晶格了),因此製造人員進入無塵室前,都必須事先清洗身體、穿戴防塵衣、全副武裝採取預防措施。晶圓製造環境更比手術室乾淨十萬倍。

晶圓會在無塵的狀態下送到無塵室並分裝到密封的容器中,進行隨後的生產步驟。

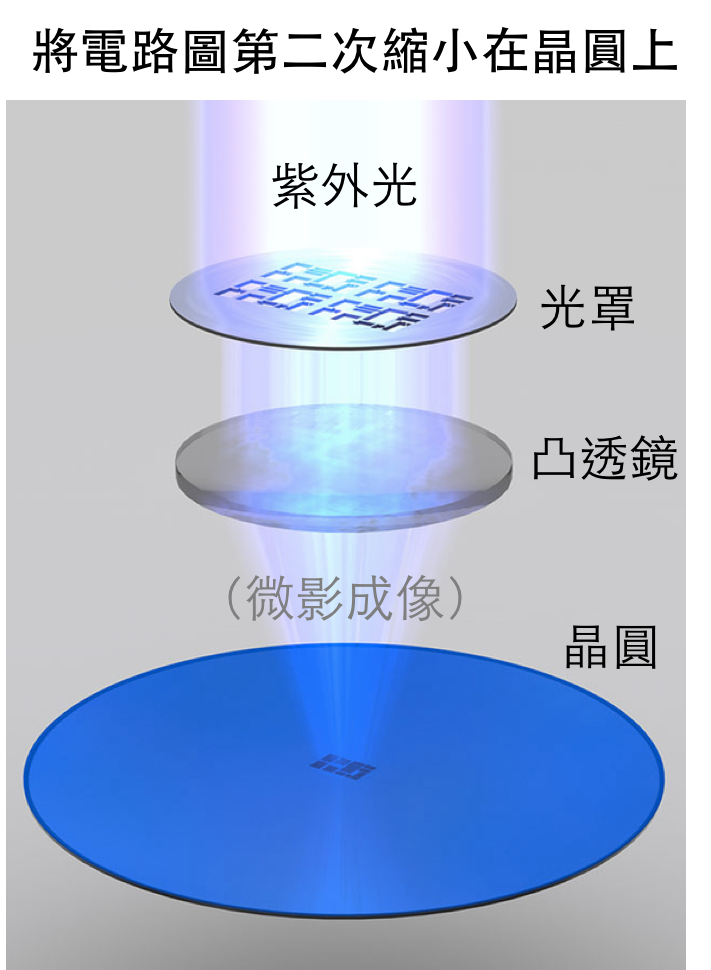

三. 建築成形: 光罩製作 (光蝕刻與微影成像)

我們在先前提到,積體電路 (IC) 跨時代的意義在於,工業界不用各自生產電子件再組建起來,可以一口氣將電路板依據電路圖生產出來。這是怎麼做到的呢?

答案是:光學攝影技術。一大張的電路設計圖,要縮小並壓印到矽晶圓(基板),靠的就是光學原理。

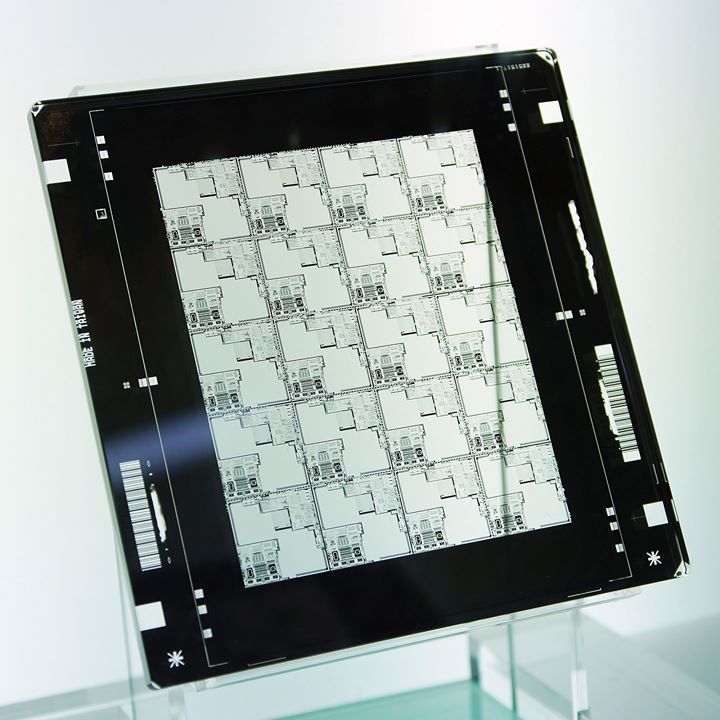

首先光罩廠會將IC設計圖形第一次縮小,以電子束刻在石英片上,成為光罩。

光罩

由於電子束的寬度是1微米,所以光罩上依據設計圖所刻出的半導體迴路也是1微米寬。接下來光罩廠會將完成的光罩送進晶圓廠。

晶片製造,也就是將光罩上刻的設計圖、第二度縮小至晶圓上。與底片洗出相片的原理一樣,「光罩」就是照相底片、「晶圓」就是相片紙。

晶圓上面會事先塗上一層光阻 (相片感光材料),透過紫外光的照射與凸透鏡聚光效果、會將光罩上的電路結構縮小並烙印在晶圓上,最後印在晶圓上的半導體迴路會從光罩的 1 微米、變為 0.1 微米。陰影以外的部分會被紫外光破壞,隨後能被沖洗液洗掉。

藉由光蝕刻與微影成像,晶圓廠成功將設計圖轉印到微小的晶圓基板上。如同底片品質會影響照片成像的好壞,光罩上圖形的細緻度是晶片品質的關鍵。

光刻製程結束後,工程師會在晶圓上繼續加入離子。透過注入雜質到矽的結構中控制導電性,與一連串的物理過程,製造出電晶體。其過程相當複雜,甚至需要像兩個足球場大的無塵室。

待晶圓上的電晶體、二極體等電子元件製作完成後,工程師會將銅倒入溝槽中形成精細的接線,將許多電晶體連結起來。

在指甲大的空間裡,數公里長的導線連接了數億個電晶體,製作成大型積體電路。至此,偉大的建築就完成了。

四. 成品包裝: 封裝與測試

晶圓完成後被送到封裝廠,會切割成一片片的「裸晶」,如先前圖所示。由於裸晶小而薄、非常容易刮傷,故封裝廠會將裸晶安裝在導線架上、在外面封裝上絕緣的塑膠體或陶瓷外殼,剪下來印上委託製造公司的標誌。

最後進行測試,進行晶片結構及功能的確認、將不良品挑出,一顆晶片就大功告成了!

半導體大廠有哪些?

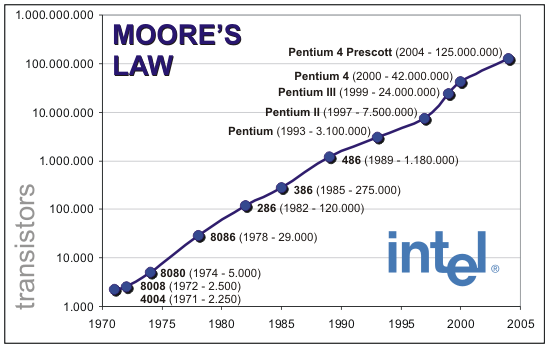

1960年代積體電路的發明,讓許多的半導體元件可以一次放在一塊晶片上。隨著半導體的縮小,IC上可容納的電晶體數目,約每隔兩年便會增加一倍、性能每18個月能提升一倍 。

從1960年代不到10個,1980年代增加到10萬個、1990年代增加到1000萬個。這個現象由英特爾的名譽董事長摩爾所提出,稱為摩爾定律 (Moore’s Law)。如今,積體電路上的元件高達數億至數十億個。

早期,半導體公司多是從IC設計、製造、封裝、測試到銷售都一手包辦的整合元件製造商(Integrated Device Manufacturer, 俗稱IDM),如英特爾 (Intel)、德州儀器 (TI)、摩托羅拉 (Motorola)、三星 (Samsung)、菲利普 (Philips)、東芝 (Toshiba),以及國內的華邦、旺宏。

然而,由於摩爾定律的關係,半導體晶片的設計和製作越來越複雜、花費越來越高,單獨一家半導體公司往往無法負擔從上游到下游的高額研發與製作費用。

因此到了1980年代末期,半導體產業逐漸走向專業分工的模式──有些公司專門設計、再交由其他公司做晶圓代工和封裝測試。

其中的重要里程碑莫過於1987年台積電 (TSMC) 的成立。

由於一家公司只做設計、製程交給其他公司,容易令人擔心機密外洩的問題 (比如若高通和聯發科兩家彼此競爭的IC設計廠商若同時請台積電晶圓代工,等於台積電知道了兩家的秘密),故一開始台積電並不被市場看好。

然而,台積電本身沒有出售晶片、純粹做晶圓代工,更能替各家晶片商設立特殊的生產線,並嚴格保有客戶隱私,成功證明了專做晶圓代工是有利可圖的。

如今台積電是全球排名第一的晶圓代工公司。知名廠商亦包括全球排名第二的聯電 (UMC)、格羅方德 (GlobalFoundries)、中芯 (SMIC)。

由於 IC 設計公司只設計和銷售晶片,但將製造、封裝、測試外包給第三方、以專心投入資金與人力研發,故被稱為無廠半導體 (Fabless Semiconductor Company)。

包括高通 (Qualcomm)、博通 (Broadcom)、聯發科 (MediaTek),與中國紫光集團下的展訊 (SpreadTrum)。

最後,台灣半導體封裝大廠日月光(ASE)排名全世界第一,全球市占近20%。排名第二為美商艾克爾(Amkor)、第三亦為台灣廠商矽品(SPIL)。

半導體產業在近數十年來的發展速度不只驚人,許多重大的創新也支持了眾多其他產業也、產生了極大的影響,可以說是數位時代之母。毫無疑問地,在未來,半導體的應用與產業規模,將會比今日來的更加廣泛且舉足輕重。

最後為大家輕鬆總結一下我們這篇已經提到的知識,同時看看還有哪些知識雖然在本篇文章中沒有提到、但同樣很重要的,預告一下會在下篇出現:

- 感謝熱心讀者補充:

- 電路設計圖是 IC 設計廠在看的,晶圓代工廠拿到的會是經轉換過的線路 Layout 設計圖,也就是 Layout GDS 檔。.gds 檔案格式的副檔名的意思是與 Chip Layout Information 相關的模擬 CAD 檔案。(CAD 指用電腦軟體模擬實物設計)

- 電路設計圖轉換成 Layout 圖時,會根據各家代工廠的 Design Rule 而有所不同。各家代工廠的 Design Rule 是和該代工廠自家的製程能力與製程方式而有所差異。

- 微影成像完後,嚴格上來說圖形是還沒轉換到晶圓上的,此時只是把圖形轉換到光阻上(就是內文比喻的底片),之後經過乾蝕刻往下挖挖挖,才會把圖形轉印到晶圓上。