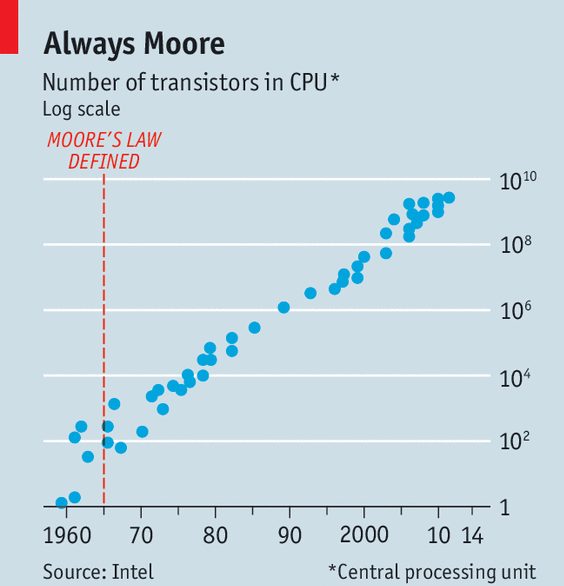

摩爾定律是由 Intel 創始人之一的 Gordon Moore 所提出來的:「積體電路 (IC) 上可容納的電晶體數目,約每隔兩年便會增加一倍。」而 Intel 執行長 David House 更曾言:「約每 18 個月,晶片的效能將提高一倍 (即更多的電晶體使其更快)。」

半導體行業大致按照摩爾定律發展了半個多世紀,對二十世紀後半葉的世界經濟增長做出了貢獻,並驅動了一系列科技創新、生產效率的提高和經濟增長。個人電腦、網際網路、智慧型手機等技術改善和創新都離不開摩爾定律的延續。

由於現代電腦、手機與家電的 CPU 、GPU 等許多零件,都是以電晶體 (Transistor) 為基本元件製成的積體電路 (Integrated Circuit)。要瞭解電腦的大腦── CPU 運作的基本原理,有關邏輯電路的基礎知識便十分重要。

先前我們在 為什麼電腦是只有 0 與 1 的世界?世界上只有 10 種人,一種是懂二進位的 一文中介紹了 AND、OR、NOT 等邏輯閘,和要怎麼用邏輯閘建立出邏輯電路來實現運算。

然而我們卻還沒介紹「邏輯閘是怎麼建構出來的」和「電晶體的功用是什麼」這兩個重要的問題。今天就讓我們來瞭解一下,如何利用電晶體來建立出邏輯閘吧!

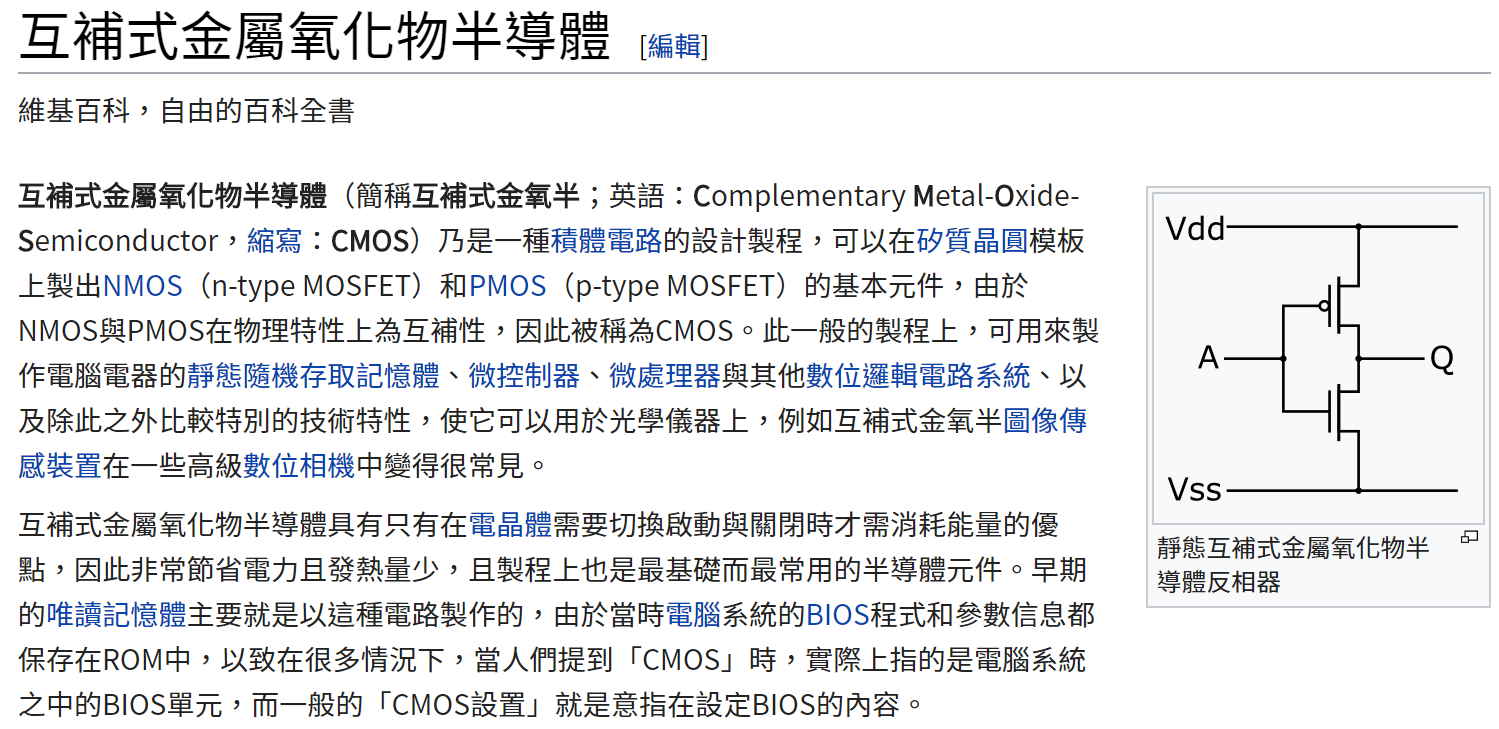

一天到晚聽到半導體、CMOS、電晶體等名詞,卻搞不懂它的意義或功能嗎?來個簡單的小測試:

如果你看得懂以上「CMOS」在維基百科的說明文字,包括 NMOS、PMOS,還有左方反相器 (Inverter) 的示意圖,歡迎關閉離開這篇文章。若不太理解… 今天這篇文章的任務很簡單,保證閱讀完畢後一看就懂。讓我們開始吧!

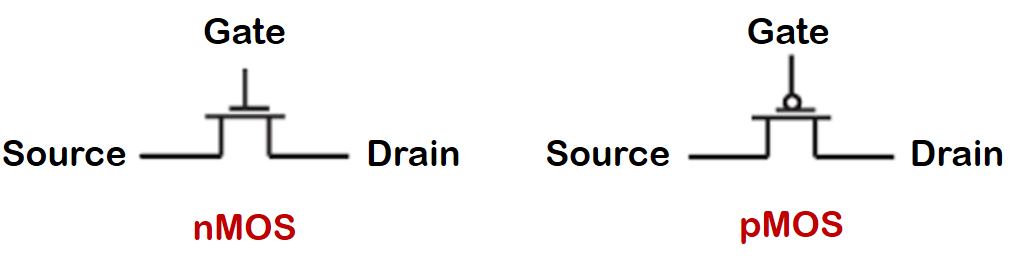

目前製作電晶體主流技術是採用一種稱為「金氧半場效電晶體」 (Metal-Oxide-Semiconductor Field-Effect Transistor)的技術,採用這個名稱的原因是因為其中包含一層氧化層,而閘極 (Gate) 上可能會採用金屬作為材質 (但不一定要用金屬)。

因此又可稱 MOSFET、MOS 電晶體。MOS 電晶體主要又分成兩種類型,一種為 nMOS 電晶體、一種為 pMOS 電晶體。

圖為 nMOS 電晶體和 pMOS 電晶體的電路符號

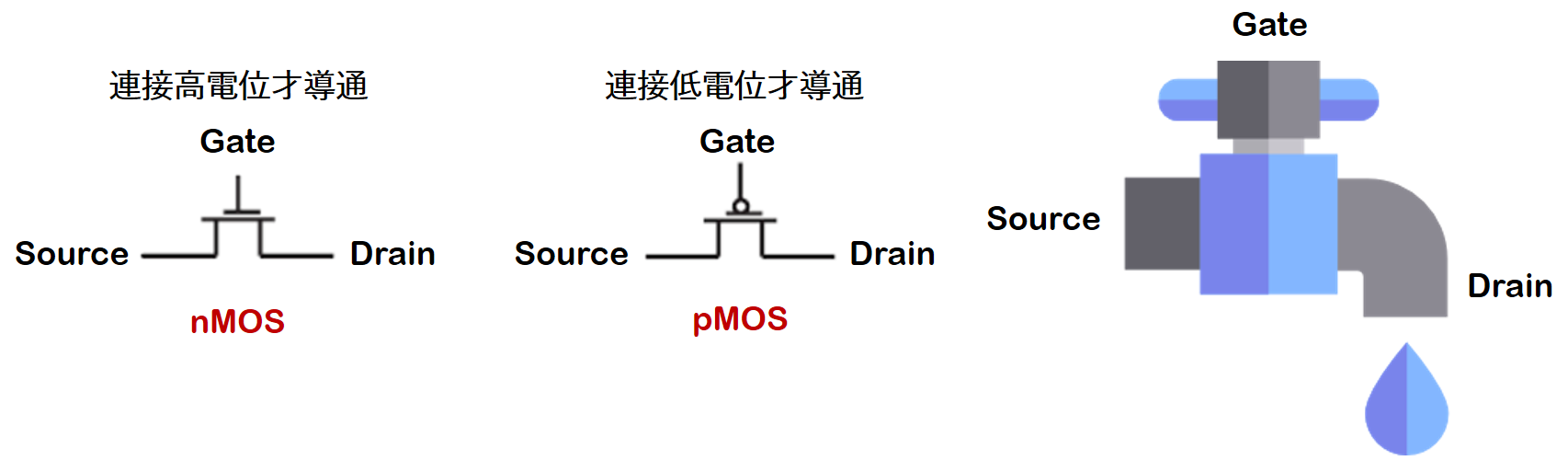

MOS 電晶體對外有三個連接:源極 (Source)、汲極 (Drain) 與閘極 (Gate)。只看這個符號可能會覺得非常抽象,讓我們舉個簡單的例子:

MOS 電晶體的工作原理和水龍頭很類似,電路中的電流就好比水管中的水流,水流的來源就是「Source」、水流出的地方稱為「Drain」,控制水流的水龍頭就是「Gate」。如果把 Gate 打開,電流就會從 Source 流到 Drain,相當於導通電晶體。

nMOS 電晶體導通的條件是在 Gate 端連接高電位;若 Gate 端連接低電位時,nMOS 電晶體就不會導通。另一方面,當 pMOS 的 Gate 端連接低電位時,電晶體會導通、連接高電位則不導通。

就好似有兩種類型的水龍頭,一種將把手向上拉才會出水、另一種將把手向下壓才會出水。

如果我們將 nMOS 與 pMOS 兩組功能互相對應的 MOS電晶體組合在一起,就能做出一種非常省電的電路,稱為 CMOS (互補式金屬氧化物半導體, Complementary Metal-Oxide-Semiconductor)。而 CMOS 也是目前實現積體電路最普遍的作法。

CMOS 雖然耗費了相當多的邏輯閘,但是省電又不容易發熱,因此廣泛被用在製作處理器、記憶體等數位邏輯電路上,因此 CMOS 在半導體產業上佔有非常重要的地位。

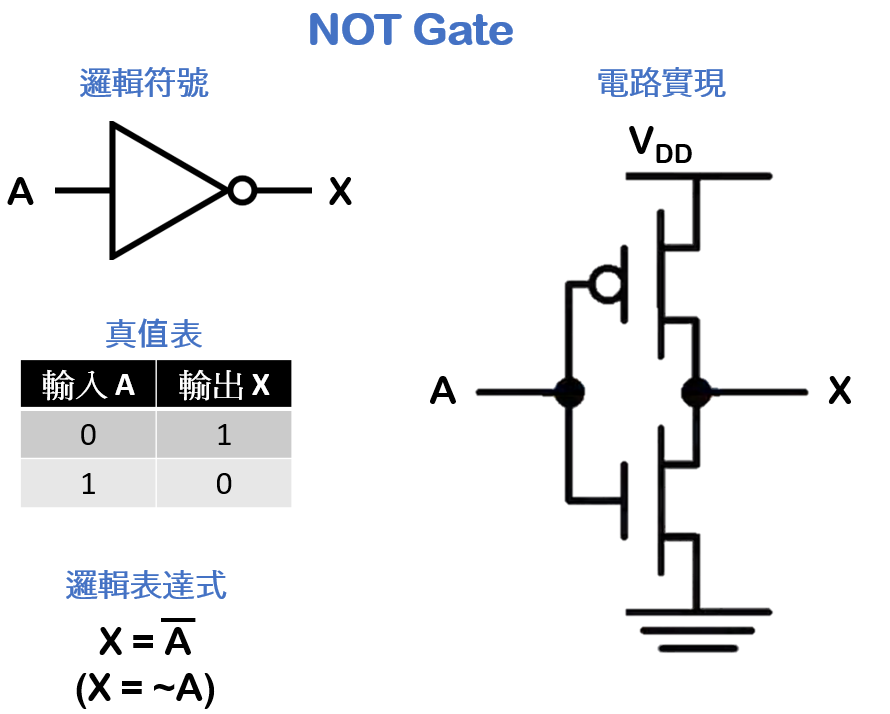

接下來,就讓我們來看看:如何用電晶體建構出邏輯閘?先從其中最簡單的一種邏輯──NOT 講起。也就是用 nMOS 和 pMOS 建構出 NOT 邏輯閘。

從圖中可看出 NOT Gate 的工作原理很簡單,只要用兩個電晶體便能實現。

電路圖中的 A 同時連接到了兩個電晶體的 Gate端,一個 nMOS 電晶體、一個 pMOS 電晶體。

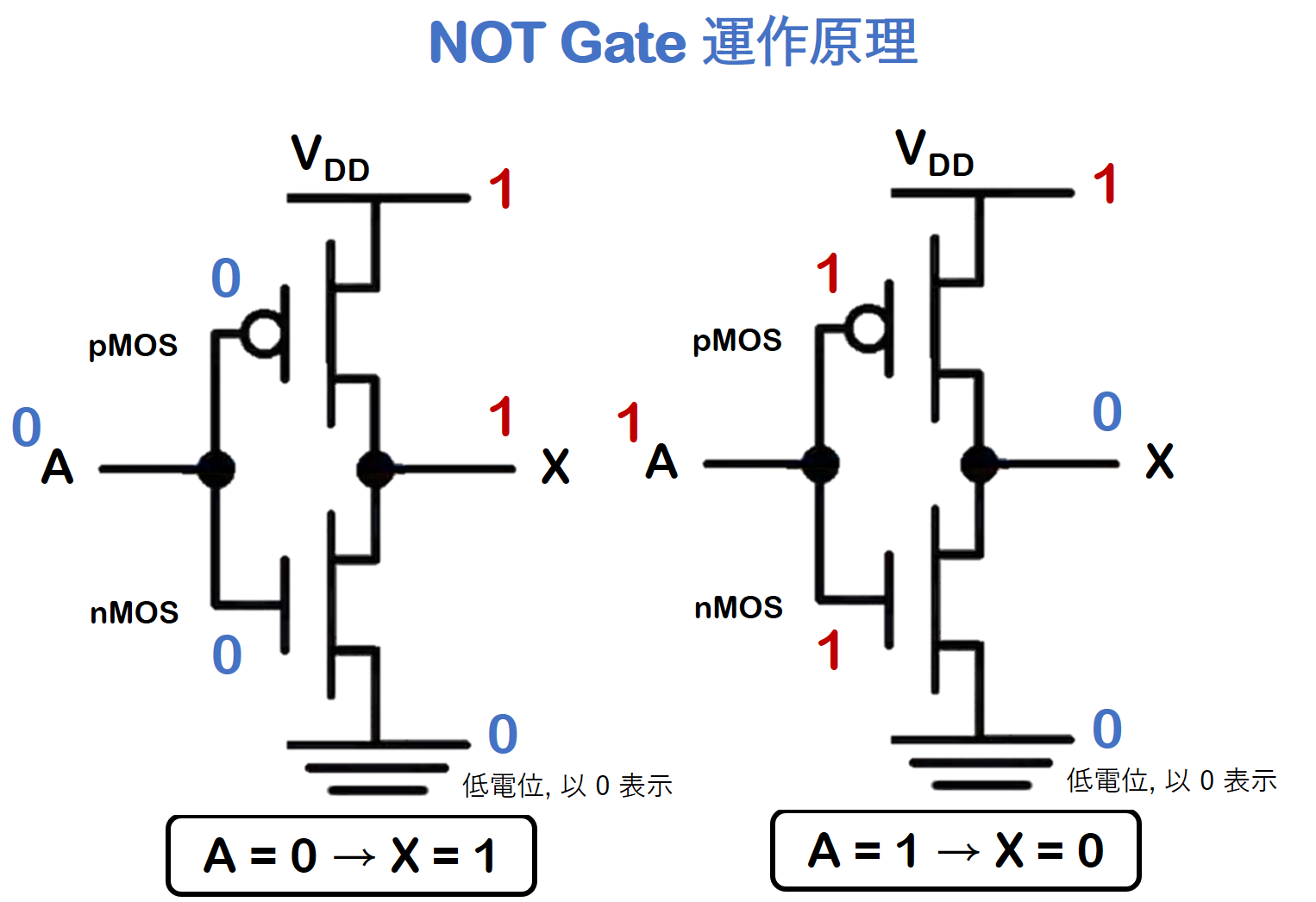

當 A 為 0 時,對於 pMOS 電晶體來說、它的 Gate 端為 0 時是導通的,所以電源這一端的 1 就能傳導過來;同時,nMOS 的 Gate 端連接 0 時是不導通的。所以最後 X 這條電路就接到 1。

這就是 NOT 邏輯閘使輸入電路 A 為 0、輸出電路 X 為 1 的運作原理。

同理,電源是 1、低電位是零,當 A 為 1 時,上面 pMOS 的 Gate 端是1,所以處於關閉狀態。而下面 nMOS的 Gate 端為 1 時,就處於導通狀態,此時 X 的輸出就是 0。

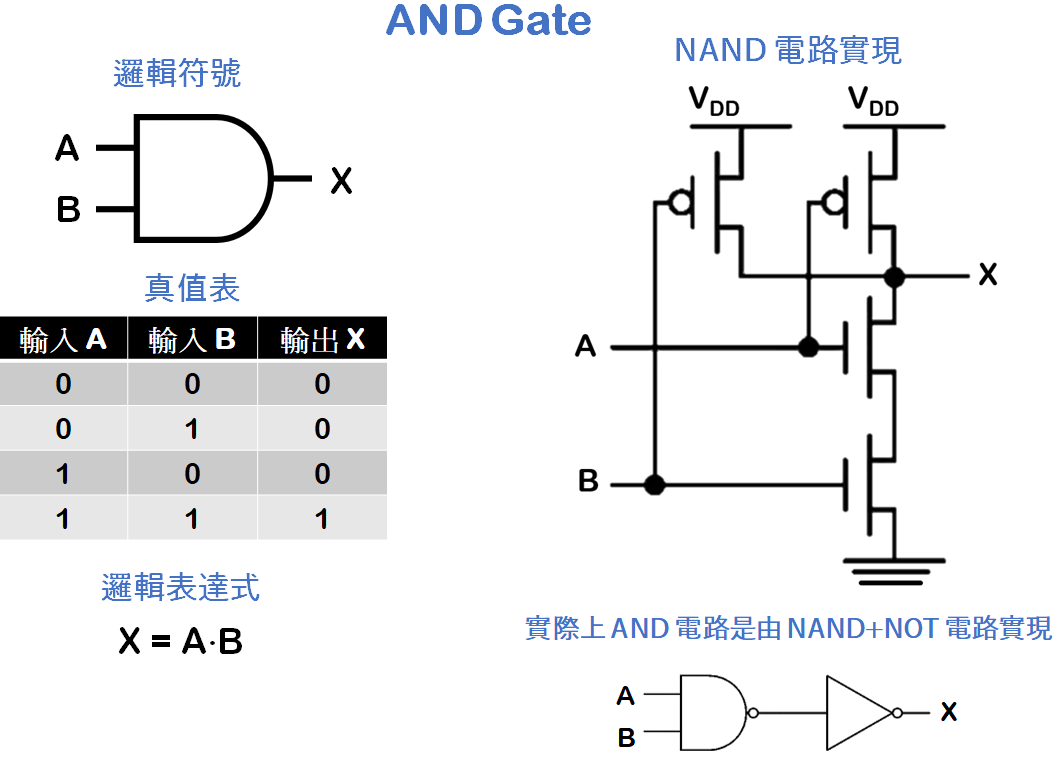

接著,讓我們來看看 AND 邏輯閘的實現原理。

右邊的電路圖為 NAND 電路原理,其中包含四個電晶體。NAND 邏輯閘的真值表和 AND 相反,為 AND 再取 NOT 的結果。我們需要的功能雖然是 AND 邏輯閘,在這邊為什麼卻不放 AND 電路圖,而是放一個 NAND 呢?

這是因為實際上 NAND 邏輯閘的實現方式比 AND 邏輯閘更簡單,所以通常會用一個 NAND 加上一個 NOT,就能很簡單地實現 AND 邏輯閘的功能。

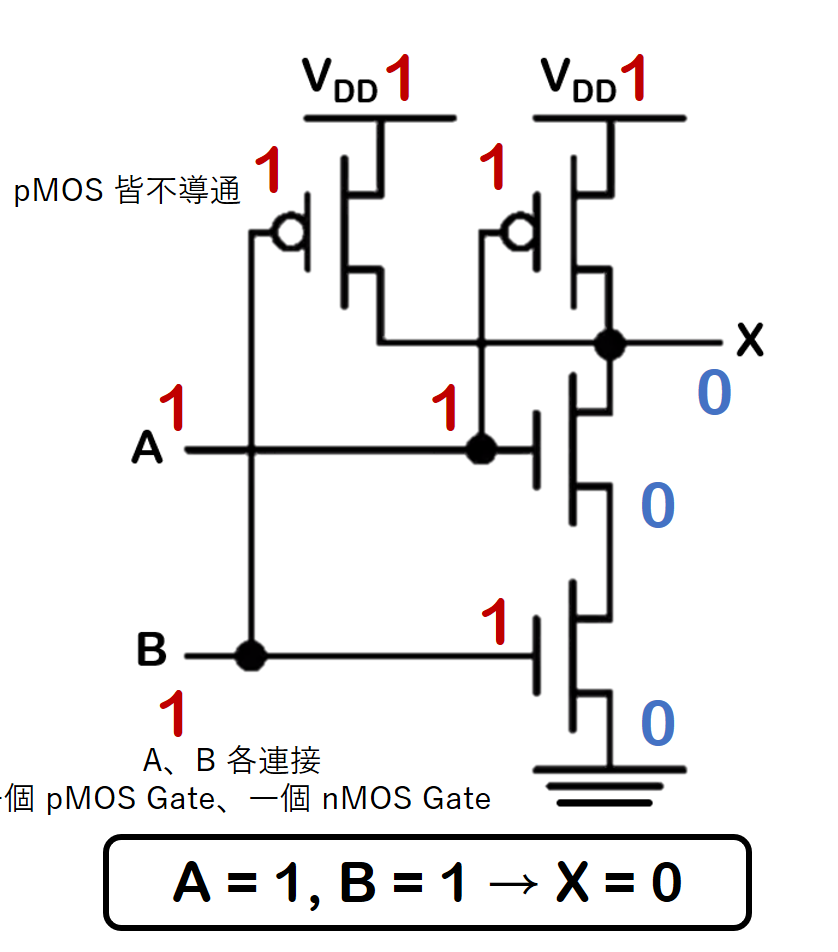

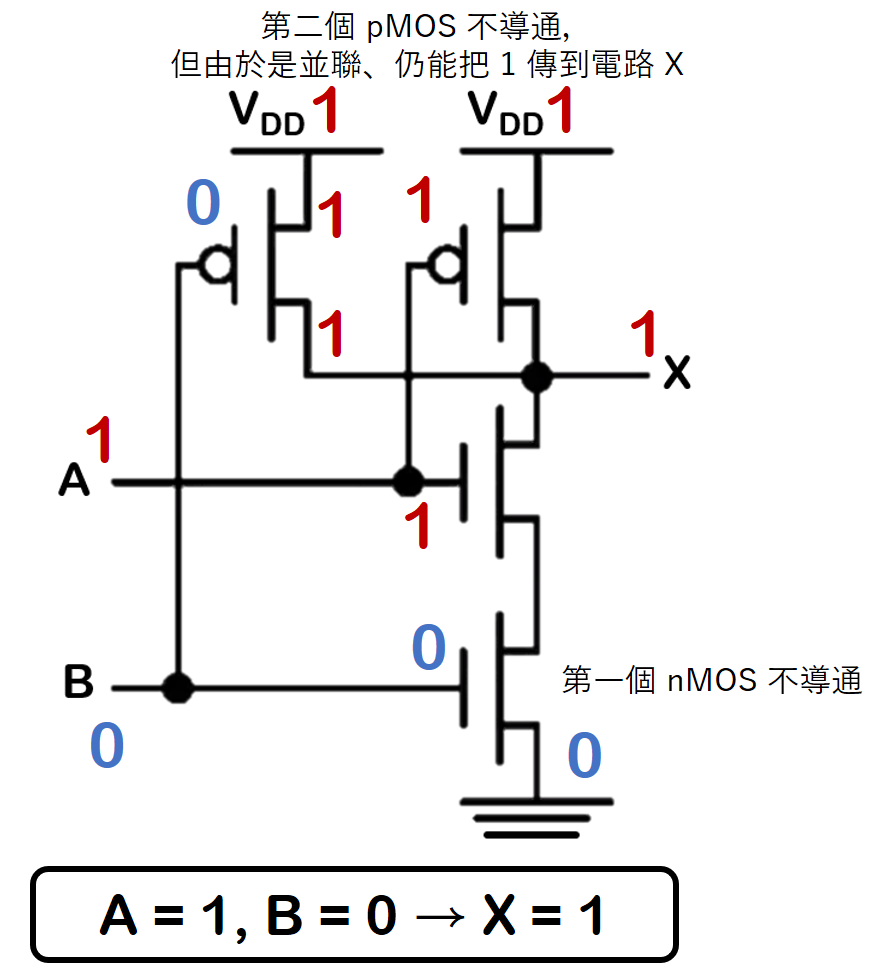

A、B 各連接了一個 pMOS Gate、一個 nMOS Gate。

當 B 等於 1 時,B 連接的 pMOS Gate (左上方第一個電晶體) 不會導通;同時,B 連接的 nMOS Gate(右下方電晶體) 由於 Gate 端為 1 時會導通,即把 0 傳遞過來。

同理,A 連接的 pMOS Gate 不會導通、nMOS 繼續導通將 0 傳給電路 X,最後輸出即為 0。

也就實現了 NAND 電路:A = 1, B = 1 → X = 0 的目標。

讀者可以自己試著畫畫看 A 、 B 的其他三種輸入,應該能出現 NAND 全部的輸出結果。以下為示意圖:

另外,還有 OR 邏輯閘、XOR 邏輯閘…。事實上,所有的邏輯線路都可以用 NAND 來合成,NAND 也被人稱作萬用邏輯閘。

用一個 NAND 邏輯閘,就能做出NOT、AND、OR 等邏輯閘

最後的最後,帶大家重新看看 CMOS 的維基百科說明。 NMOS 和 PMOS 已經為大家介紹過了;而左邊那張圖… 你發現了嗎?事實上就是「NOT 邏輯閘」,也就是「用 NMOS 和 PMOS 組出的 NOT 電路圖」。NOT 邏輯閘的另一個名字也叫 Inverter。

不要被 靜態互補式金屬氧化物半導體反相器… 這一長串咒語騙到啦!翻成英文就只是 CMOS Inverter (NOT logic gate),此圖只是取所有 CMOS 邏輯閘中、最簡單實現的一種來作 CMOS 的範例。

今天的解說就到這邊!希望這篇文章有幫助到正在瞭解半導體產業名詞的你 🙂