生活中不論是手機、電腦還是資料中心的伺服器,其中的數據都仰賴半導體晶片進行運算,過去十幾年晶片效能都靠著半導體製程的改進而成長:透過更先進的製造工藝,在相同單位面積的晶片上置入更多的電晶體,藉此在體積不增加的前提下提升晶片的效能與功耗表現。

當半導體先進製程邁入 7奈米(nm) ,展望 5nm ,電晶體大小不斷接近原子的物理體積限制,電子及物理的限制也讓先進製程的持續微縮與升級難度越來越高,而為了要跳脫瓶頸,投資在研發的成本也隨之呈跳躍式的成長,使得晶片的效能陷入成長趨緩的態勢,許多分析師甚至因此認定半導體業不久即將面臨成長瓶頸,過去被認為堅不可摧的「摩爾定律」也即將告終。

事實上,業界早已轉向尋找其他的可能性,解決辦法就是從晶片的布局設計著手,例如將原先單層的晶片朝向多層晶片堆疊發展,也就是廣義上的「3D 晶片設計」,例如英特爾(Intel)便發展出「Foveros 架構」:將 CPU 、 GPU 、記憶體以及連接介面進行三維堆疊,能更有效率利用空間,讓晶片在同樣的效能下,有更小的體積並消耗更少的電力。

另一方面,台積電也在今年完成了首顆 3D 晶片的封裝作業──長遠而言,發展多維度的晶片設計架構已經成為趨勢,全球半導體產業致力尋找後摩爾定律時代的突破口,而除了單純從平面到3D的晶片設計,產業界也正積極從其他方式著手提升晶片效能,其中「異質整合路線圖(Heterogeneous Integration Roadmap)」是最受關注的一項發展方向。

異質整合技術:從同質多晶片到異質多晶片封裝

所謂的「異質整合(Heterogeneous Integration)」,定義上是透過 2.5D 及 3D 等多維度空間設計,將多個不同性質的電子元件整合進單系統級封裝中(System in Package, SiP),不像過去封裝個別的晶粒而成單一功能的IC,當「異質整合」成為產業技術的主流趨勢,封裝範圍已不僅限個別晶粒(Die),還包括微機電系統(MEMS)、被動元件、獨立晶片及多項電子系統,成品為一個具體而微的多功能高階晶片。

舉個例子,高通的驍龍行動處理器(Snapdragon)是一種系統單晶片(System on Chip, SoC),以 2D 或是 2.5 D 的架構整合了多項數位微處理器,像是 CPU 、 GPU 、 RAM 以及 Modem ,成功縮小晶片組的體積,達到智慧型手機對體積的嚴苛要求,但整合範圍僅限同性質的數位訊號晶片,單一晶片僅有數位運算功能。

「異質整合」則進一步擴大整合的範圍:除了數位訊號晶片,還將封裝範圍延伸到不同性質的類比晶片與微電子系統,包含光源感測器、微機電麥克風、射頻天線、生物感測器等晶片元件都被包進同一個封裝單位,讓單一晶片本身便具有運算、光感測、收音、錄音、通訊與生物辨識等多項功能。

賦予單一晶片多功能與體積優勢

為何異質整合特別? 智慧型手機為因應消費者需求需同時具備多項功能,因此需要大面積的主機板連結多個晶片,才能組成一支正常運作的手機,而整個主機板就占據手機 40% 以上的面積,導致智慧型手機的尺寸很難再趨輕薄短小。

透過「異質整合」,不須透過主機板連接多項電子元件,多種不同性質的元件都能被封裝成「單一晶片」,不但能縮減大量的體積,還能依照不同應用場域的需求擴充晶片的功能,例如同時將數位晶片、類比晶片、感測器以及天線等異質元件透過整合成為單一晶片,這個集合晶片能獨立執行多項功能,晶片之間的物理距離減少也會降低訊號傳輸的耗電量與延遲時間,一次滿足省電節能與效率提升的需求。

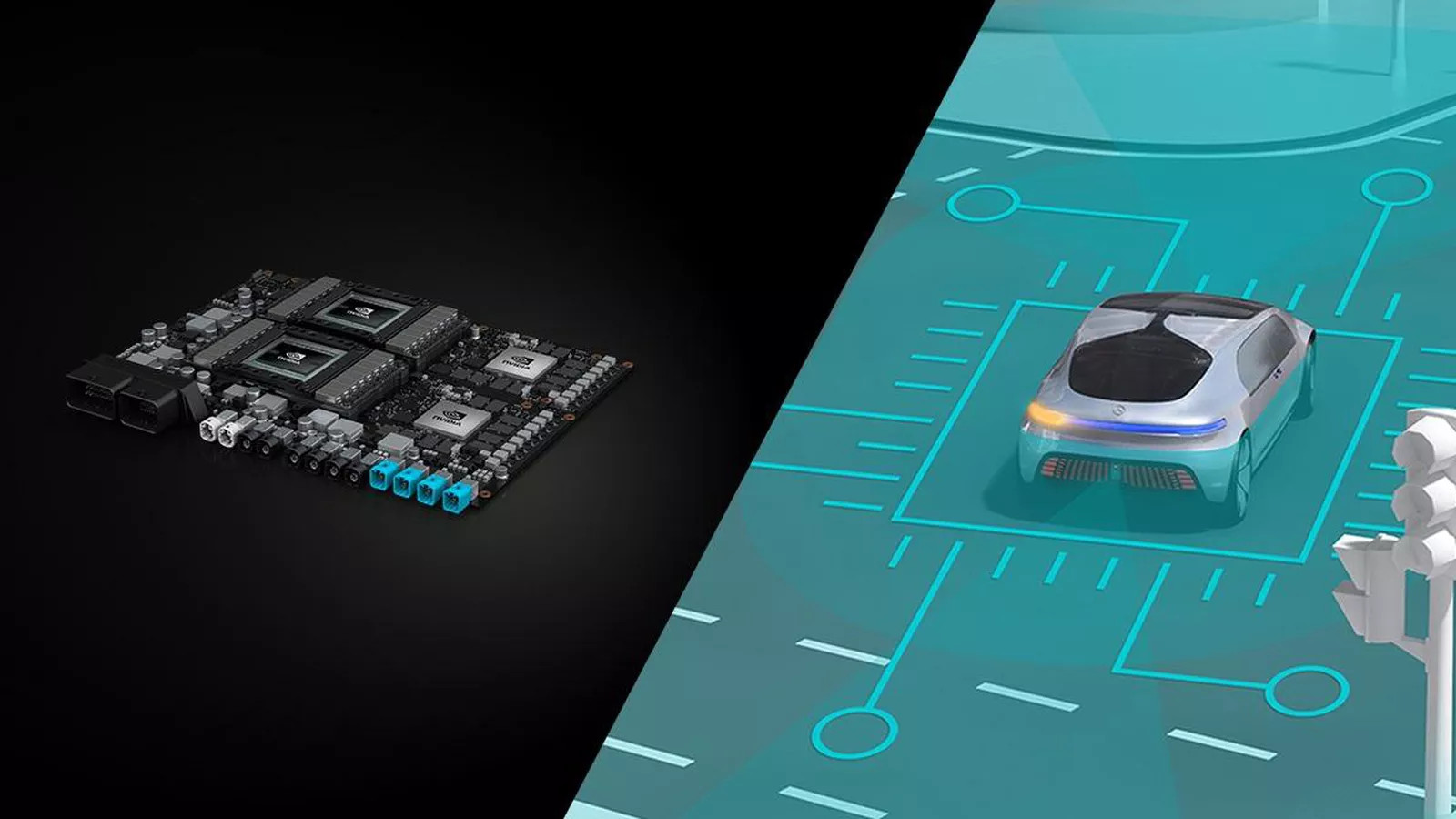

一般而言,科技產業向來是「商業應用」帶動「硬體發展」,隨著數據時代來臨, 5G、物聯網、量子電腦、人工智慧等科技應用正推高運算效能的門檻,除了滿足數據的採集、分析與運算的需求之外,晶片設計上也必須依據領域不同而提高調整彈性。

舉例來說,物聯網晶片的工作環境複雜,需要在各式各樣難以維護的環境下長時間運作,必須使用多功能且高效能的晶片進行數據採集與邊緣計算,低功耗以及通訊的穩定度這時就顯得相當重要,如果晶片設計公司可以透過精進「異質整合技術」,成功在維持高良率的前提下整合多項不同晶片來擴充單一晶片功能,便能打造出體積小、效能高、在各種場景的終端應用皆能發揮強大功能的單一晶片。

步入後摩爾定律時代,未來半導體產業不只追求製程上的持續微縮,更在體積、耗能與數據運算架構的設計上都需要進一步的突破,而「異質整合技術」正帶領著產業探索晶片架構、運算效率,以及負載功能的全新可能性。

有鑑於異質整合已成為半導體產業持續維持成長動能的引擎之一,全球第二大國際半導體展SEMICON Taiwan今年將從先進封裝、測試、化合物半導體、矽光子等角度切入,規劃異質整合主題展區及舉辦多元活動,並同期舉辦「SMC Taiwan策略材料高峰論壇」、「SiP Global Summit系統級封測國際高峰論壇」,分別探討異質整合在先進封裝技術及創新材料上的機會與挑戰。想進一步了解異質整合技術未來的技術發展與應用市場,現在起可免費報名9月18至20日的SEMICON Taiwan,絕對不能錯過!